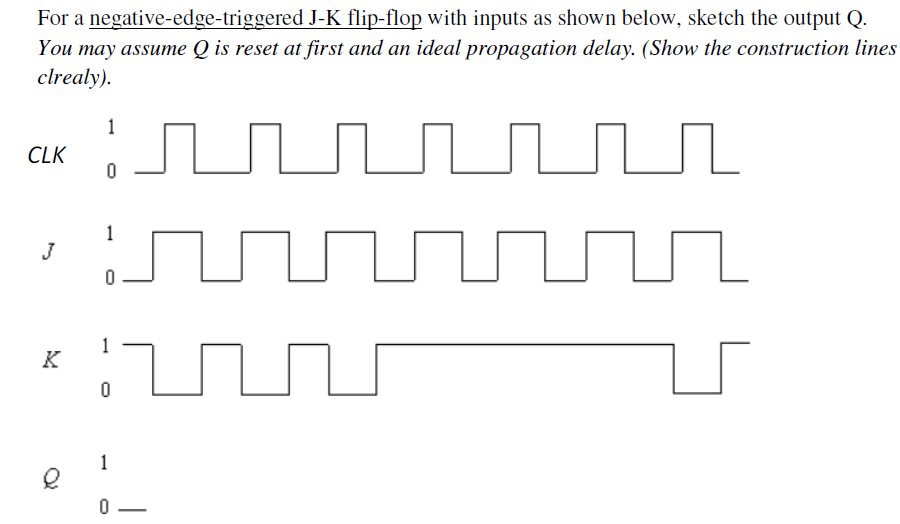

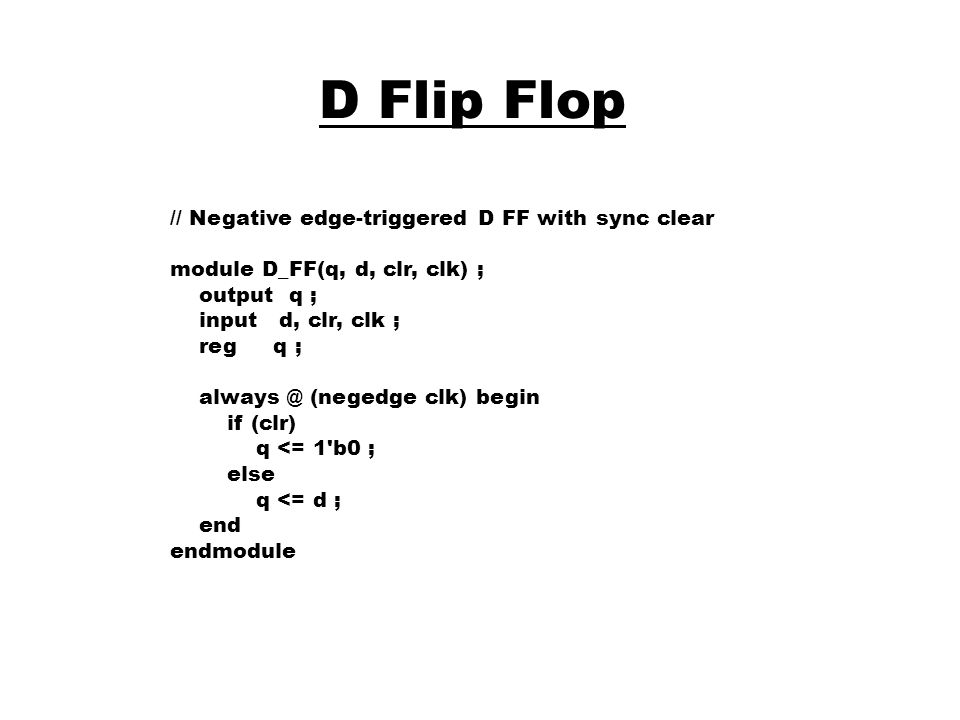

So my question is, is making a D-flip flop with asynchronous level triggered reset possible or not? Both in verilog and in digital logic. (Source: Synthesis and Simulation Design Guide, UG626, Oct 19, 2011) Notice that this is basically the same as your second example (except using the opposite clock edge).

Since that would require multiple sources to drive q, again problem at RTL synthesis. Heres Xilinxs example of a 'Flip-Flop with Negative Edge Clock and Asynchronous Reset': always (negedge C or posedge CLR) begin if (CLR) Q < 1’b0 else Q < D end. If the number of signals is more than one, then besides the clock the other signals are asynchronous set and/or reset. In the above example, the clock sig1 is rising edge triggered.

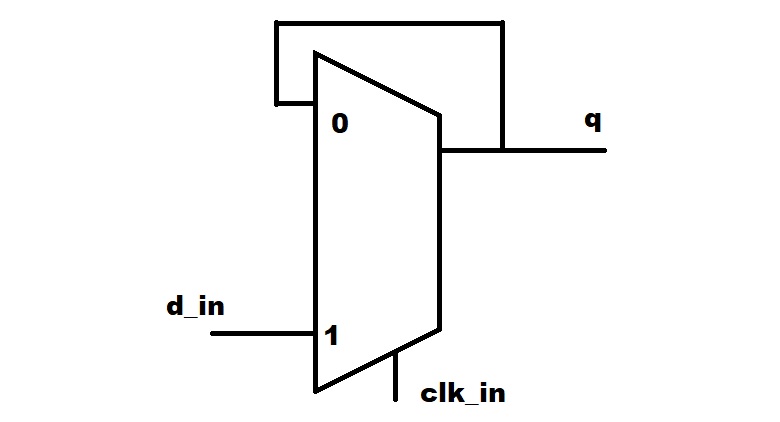

Or making a D flip flop with synchronous edge triggered reset like this always clk or posedge clr)īut how can I make a level triggered but asynchronous reset? I cannot do always clk or clr)īecause that would be oring two incompatible types, so an error will be thrown while doing the RTL synthesis. The edge on the signal indicates whether the clock is rising edge triggered or falling edge triggered. It is easy to make a D flip flop with synchronous level triggered reset like this always clk) I was experimenting with behavioral modeling and ended up having this problem.

But I just hit a brick wall with this one. I think I have the basics down perfectly. I am starting to learn verilog coding in college and didn't have that much of a problem till now.

0 kommentar(er)

0 kommentar(er)